- 您现在的位置:买卖IC网 > Sheet目录308 > ADUM3160BRWZ-RL (Analog Devices Inc)IC ISOLATOR USB 2.5K 16SOIC

ADuM3160

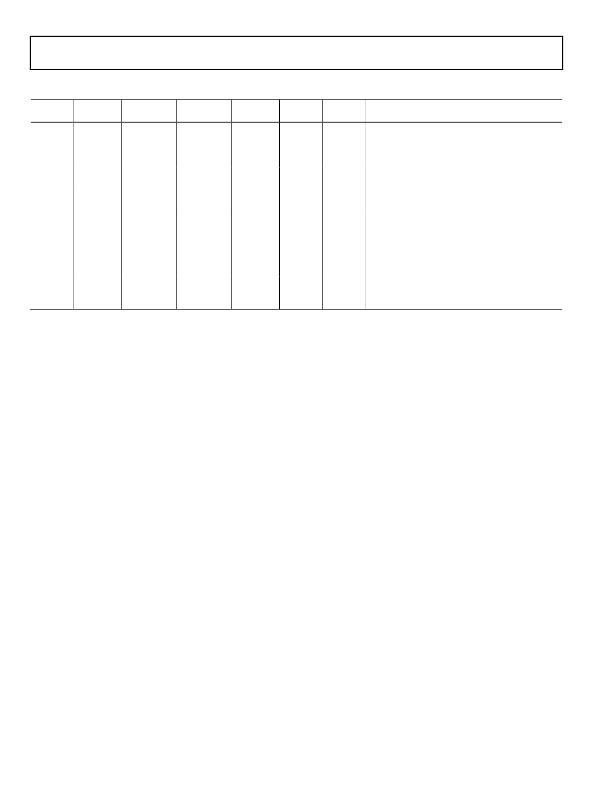

Table 10. Truth Table , Control Signals, and Power (Positive Logic)

Data Sheet

V SPU

Input 1

High

V UD+ , V UD?

State 1

Active

V BUS1 , V DD1

State

Powered

V BUS2 , V DD2

State

Powered

V DD+ , V DD?

State 1

Active

V PIN

Input 1

High

V SPD

Input 1

High

Description

Input and output logic set for full speed logic

convention and timing.

Low

Low

High

Active

Active

Active

Powered

Powered

Powered

Powered

Powered

Powered

Active

Active

Active

High

High

High

Low

High

Low

Input and output logic set for low speed logic

convention and timing.

Not allowed. V SPU and V SPD must be set to the same

value. The USB host detects a communication error.

Not allowed. V SPU and V SPD must be set to the same

value. The USB host detects a communication error.

X

X

Z

X

Powered

Unpowered

Powered

Powered

Z

Z

Low

X

X

X

Upstream Side 1 presents a disconnected state to

the USB cable.

When power is not present on V DD1 , the down-

stream data output drivers revert to the high-Z

state within 32 bit times. The downstream side

initializes in the high-Z state.

X

Z

Powered

Unpowered

X

X

X

When power is not present on V DD2 , the upstream

side disconnects the pull-up and disables the

upstream drivers within 32 bit times.

1

X is don’t care; Z is the high impedance output state.

Rev. C | Page 8 of 16

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADUM3201WCRZ

ISOLATOR DGTL 25MBPS 2CH 8SOIC

ADUM3210WCRZ

IC DIGITAL ISOLATOR 2CH 8-SOIC

ADUM3300CRWZ

IC DIGITAL ISOLATOR 3CH 16-SOIC

ADUM3400BRWZ

IC DIGITAL ISOLATOR 4CH 16-SOIC

ADUM3442CRWZ-RL

IC DIGITAL ISOLATOR 4CHAN 16SOIC

ADUM4223BRWZ

ISOLATOR DIGITAL

ADUM4402CRWZ

IC DIGITAL ISOLATOR 4CH 16-SOIC

ADUM5000ARWZ-RL

IC DIG ISOLATOR W/DC-DC 16SOIC

相关代理商/技术参数

ADUM3160WBRWZ

功能描述:USB Digital Isolator 2500Vrms 2 Channel 12Mbps 25kV/μs CMTI 16-SOIC (0.295", 7.50mm Width) 制造商:analog devices inc. 系列:iCoupler? 包装:管件 零件状态:有效 技术:磁耦合 类型:USB 隔离式电源:无 通道数:2 输入 - 输入侧 1/输入侧 2:2/2 通道类型:双向 电压 - 隔离:2500Vrms 共模瞬态抗扰度(最小值):25kV/μs 数据速率:12Mbps 传播延迟 tpLH / tpHL(最大值):70ns,70ns 脉宽失真(最大):- 上升/下降时间(典型值):20ns,20ns(最大) 电压 - 电源:3 V ~ 5.5 V 工作温度:-40°C ~ 105°C 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商器件封装:16-SOIC 标准包装:47

ADUM3160WBRWZ-RL

功能描述:USB Digital Isolator 2500Vrms 2 Channel 12Mbps 25kV/μs CMTI 16-SOIC (0.295", 7.50mm Width) 制造商:analog devices inc. 系列:iCoupler? 包装:带卷(TR) 零件状态:有效 技术:磁耦合 类型:USB 隔离式电源:无 通道数:2 输入 - 输入侧 1/输入侧 2:2/2 通道类型:双向 电压 - 隔离:2500Vrms 共模瞬态抗扰度(最小值):25kV/μs 数据速率:12Mbps 传播延迟 tpLH / tpHL(最大值):70ns,70ns 脉宽失真(最大):- 上升/下降时间(典型值):20ns,20ns(最大) 电压 - 电源:3 V ~ 5.5 V 工作温度:-40°C ~ 105°C 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商器件封装:16-SOIC 标准包装:1,000

ADUM3190

制造商:AD 制造商全称:Analog Devices 功能描述:High Stability Isolated Error Amplifier

ADUM3190_13

制造商:AD 制造商全称:Analog Devices 功能描述:High Stability Isolated Error Amplifier

ADUM3190ARQZ

功能描述:隔离放大器

RoHS:否 制造商:Texas Instruments 输入补偿电压:1.5 mV 共模抑制比(最小值):95 dB 带宽:60 KHz 工作电源电压:3.3 V 电源电流:8 mA 工作温度范围:- 40 C to + 105 C 安装风格:SMD/SMT 封装 / 箱体:SOP-8 封装:Tube

ADUM3190ARQZ-RL7

功能描述:隔离放大器

RoHS:否 制造商:Texas Instruments 输入补偿电压:1.5 mV 共模抑制比(最小值):95 dB 带宽:60 KHz 工作电源电压:3.3 V 电源电流:8 mA 工作温度范围:- 40 C to + 105 C 安装风格:SMD/SMT 封装 / 箱体:SOP-8 封装:Tube

ADUM3190BRQZ

功能描述:隔离放大器

RoHS:否 制造商:Texas Instruments 输入补偿电压:1.5 mV 共模抑制比(最小值):95 dB 带宽:60 KHz 工作电源电压:3.3 V 电源电流:8 mA 工作温度范围:- 40 C to + 105 C 安装风格:SMD/SMT 封装 / 箱体:SOP-8 封装:Tube

ADUM3190BRQZ-RL7

功能描述:隔离放大器

RoHS:否 制造商:Texas Instruments 输入补偿电压:1.5 mV 共模抑制比(最小值):95 dB 带宽:60 KHz 工作电源电压:3.3 V 电源电流:8 mA 工作温度范围:- 40 C to + 105 C 安装风格:SMD/SMT 封装 / 箱体:SOP-8 封装:Tube